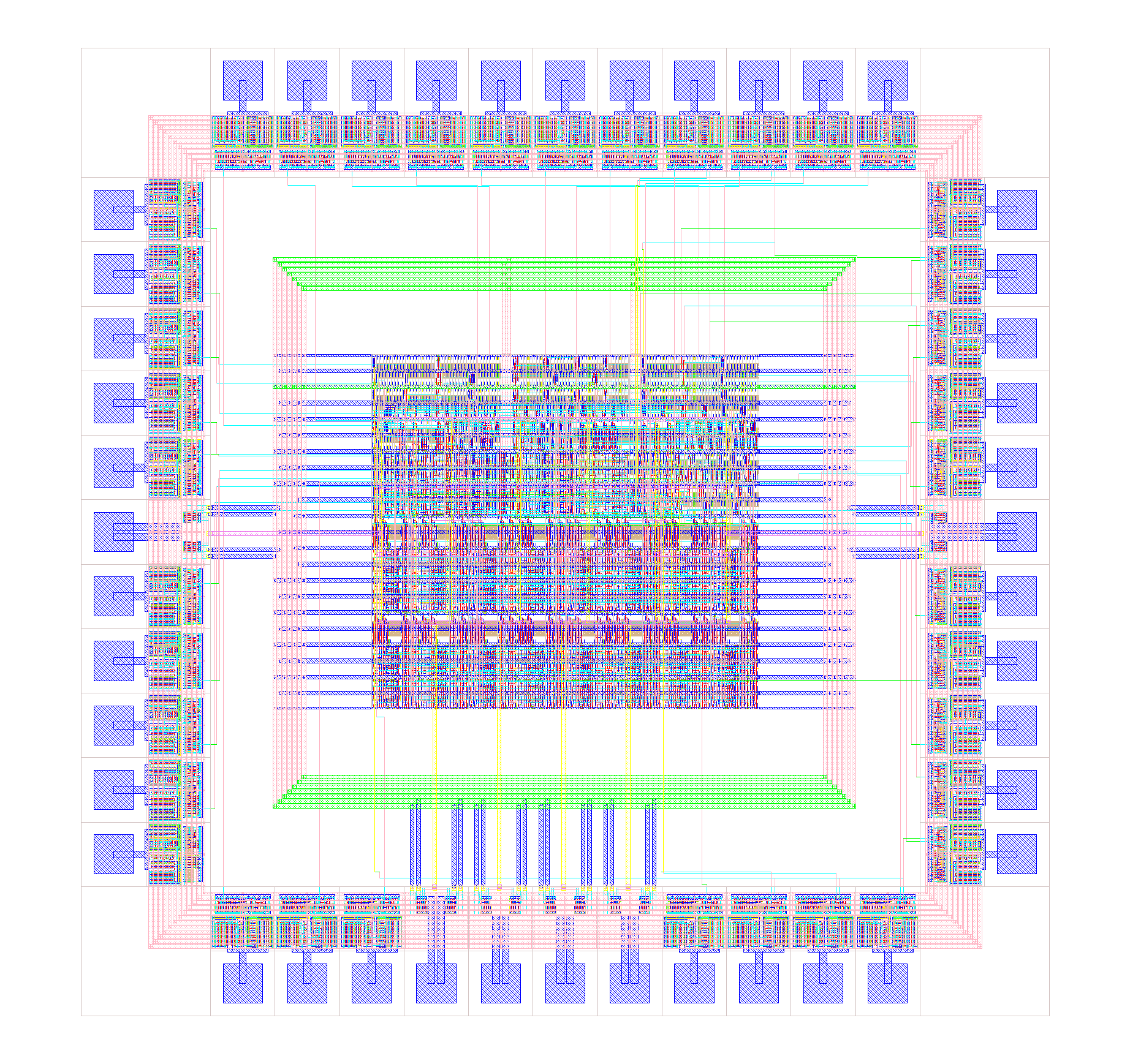

Alliance is a complete toolchain for vlsi design. It provides a vhdl compiler and simulator, logic synthetiser, automatic place & route and portable cmos library. It has been in used in research projects such as the 875K transistors StaCS superscalar microprocessor or the 400K transistors ieee gigabit hsl router. It has been actively developped during the 1990-2000 years and is maintained since. It's practical limit for one standard cell block (flat) is about 10K gates, above that limit you would need to use hierarchy and manually build a floorplan. Alliance is entirely written in C.

Coriolis was started in the year 2000 as a replacement for the place & route stage of Alliance. As such it is able to handle standard cells block (flat) of at least 150K gates. It was later extended to support analog design re-implementing the methodology introduced by the cian team of lip6 / su in cairo / cairo+. The tools have been designed from the ground up to support digital only, analog only or mixed circuits. Coriolis is written in a mix of C++ and Python.

Alliance / Coriolis is free software. All source code is realeased under the GPL license, except for Hurricane which is under LGPL and the Si2 lef / def parser drivers that are under Apache License, Version 2.0.

Short introduction to Symbolic Layout.

We are also upgrading the complete design flow by replacing Alliance obsoleting tools by more advanced foss alternatives:

The Coriolis toolchain is build upon the Hurricane database.

Alliance / Coriolis tools, at the time being, are not suitable for deep submicron technological nodes (below 130nm / 180nm).

For portability across foundries, technological nodes and freedom from fondries nda, Alliance / Coriolis rely on portable layout (or scalable layout, or symbolic layout). To produce a valid gds file, you would need to use the s2r translation tool which needs a configuration file suited for the target technology, and that file is under nda. So, either should be written by you, or given to you through services like MyCMP.