# Coriolis User's Guide

## Contents

| Credits & License                              |

|------------------------------------------------|

| Release Notes                                  |

| Release 1.0.1475                               |

| Release 1.0.1963                               |

| Release 1.0.2049                               |

| Release v2.0.1                                 |

| Release v2.1                                   |

| Release v2.2                                   |

| Installation                                   |

| Fixed Directory Tree                           |

| Building Coriolis                              |

| Building the Devel Branch                      |

| Additionnal Requirement under MACOS            |

| Packaging Coriolis                             |

| Hooking up into Alliance                       |

| Setting up the Environment (coriolisEnv.py)    |

| Coriolis Configuration & Initialisation        |

| General Software Architecture                  |

| First Stage: Technology Selection              |

| Second Stage: Technology Configuration Loading |

| Configuration Helpers                          |

| ALLIANCE Helper                                |

| Tools Configuration Helpers                    |

| Hacking the Configuration Files                |

| CGT - The Graphical Interface                  |

| Viewer & Tools                                 |

|                                                |

| STRATUS Netlist Capture                        |

| The Hurricane Data-Base                        |

| Synthetizing and loading a design              |

| Etesian Placer                                 |

| Knik Global Router                             |

| Kite Detailed Router                           |

| Executing Python Scripts in Cgt                |

| Printing & Snapshots                           |

| Memento of Shortcuts in Graphic Mode           |

| Cgt Command Line Options                       |

| Miscellaneous Settings                         |

| The Controller                                 |

| The Look Tab                                   |

| The Filter Tab                                 |

| The Layers&Go Tab                              |

| The Netlist Tab                                |

| The Selection Tab                              |

| The Inspector Tab                                |  | <br> |  |  |  |  |  |  |  |  | 27 |

|--------------------------------------------------|--|------|--|--|--|--|--|--|--|--|----|

| The Settings Tab                                 |  |      |  |  |  |  |  |  |  |  |    |

| <b>Python Interface for HURRICANE / CORIOLIS</b> |  |      |  |  |  |  |  |  |  |  |    |

| Plugins                                          |  | <br> |  |  |  |  |  |  |  |  | 31 |

| Chip Placement                                   |  |      |  |  |  |  |  |  |  |  |    |

| Clock Tree                                       |  |      |  |  |  |  |  |  |  |  |    |

| Recursive-Save (RSave)                           |  |      |  |  |  |  |  |  |  |  |    |

| A Simple Example: AM2001                         |  |      |  |  |  |  |  |  |  |  |    |

## **Credits & License**

| HURRICANE     | Rémy Escassut & Christian Masson |

|---------------|----------------------------------|

| ETESIAN       | Gabriel Gouvine                  |

| STRATUS       | Sophie BELLOEIL                  |

| KNIK          | Damien Dupuis                    |

| KITE, UNICORN | Jean-Paul Снарит                 |

The Hurricane data-base is copyright© Bull 2000-2016 and is released under the terms of the LGPL license. All other tools are copyright© UPMC 2008-2016 and released under the GPL license.

Others important contributors to Coriolis are Christophe Alexandre , Hugo Clement , Marek Sroka and Wu Yifei .

The KNIK router makes use of the FLUTE software, which is copyright© Chris C. N. CHU from the lowa State University (http://home.eng.iastate.edu/~cnchu/).

#### **Release Notes**

### Release 1.0.1475

This is the first preliminary release of the CORIOLIS 2 framework.

This release mainly ships the global router KNIK and the detailed router KITE. Together they aim to replace the ALLIANCE NERO router. Unlike NERO, KITE is based on an innovating routing modeling and ad-hoc algorithm. Although it is released under GPL license, the source code will be avalaible later.

Contents of this release:

- 1. A graphical user interface (viewer only).

- 2. The KNIK global router.

- 3. The KITE detailed router.

Supported input/output formats:

- ALLIANCE **vst** (netlist) & **ap** (physical) formats.

- Even if there are some references to the CADENCE LEFDEF format, its support is not included because it depends on a library only available to Sı2 affiliated members.

### Release 1.0.1963

Release 1963 is alpha. All the tools from CORIOLIS 1 have been ported into this release. Contents of this release:

- 1. The STRATUS netlist capture language (GENLIB replacement).

- 2. The MAUKA placer (still contains bugs).

- 3. A graphical user interface (viewer only).

- 4. The KNIK global router.

- 5. The KITE detailed router.

- 6. Partially implemented python support for configuration files (alternative to XML).

- 7. A documentation (imcomplete/obsoleted in Hurricane 's case).

## Release 1.0.2049

Release *2049* is Alpha. Changes of this release:

- The HURRICANE documentation is now accurate. Documentation for the Cell viewer and CRLCORE has been added.

- 2. More extensive Python support for all the components of CORIOLIS .

- 3. Configuration is now completly migrated under Python. XML loaders can still be useds for compatibilty.

- 4. The cgt main has been rewritten in Python.

#### Release v2.0.1

- 1. Migrated the repository from **svn** to **git**, and release complete sources. As a consequence, we drop the distribution packaging support and give public read-only access to the repository.

- 2. Deep rewrite of the KATABATIC database and KITE detailed router, achieve a speedup factor greater than 20...

## Release v2.1

- 1. Replace the old simulated annealing placer MAUKA by the analytical placer ETESIAN and its legalization and detailed placement tools.

- 2. Added a Blif format parser to process circuits generated by the Yosys and ABC logic synthetizers.

- 3. The multiples user defined configuration files are now grouped under a common hidden (dot) directory .coriolis2 and the file extension is back from .conf to .py.

#### Release v2.2

1. Added JSON import/export of the whole Hurricane DataBase. Two save mode are supported: *Cell* mode (standalone) or *Blob* mode, which dump the whole design down and including the standard cells.

## Installation

#### Note

As the sources are being released, the binary packaging is dropped. You still may find older version here: http://asim.lip6.fr/pub/coriolis/2.0.

In a nutshell, building source consist in pulling the **git** repository then running the **ccb** installer.

Main building prerequisites:

- cmake

- C++11-capable compiler

- RapidJSON

- python2.7

- boost

- libxml2

- bzip2

- yacc & lex

- Qt 4 or Qt 5

Building documentation prerequisites:

- doxygen

- latex

- latex2html

- python-docutils (for reStructuredText)

Optional libraries:

• LEF/DEF (from Sl2)

For other distributions, refer to their own packaging system.

## **Fixed Directory Tree**

In order to simplificate the work of the  $\mathbf{ccb}$  installer, the source, build and installation tree is fixed. To successfully compile Coriolis you must follow it exactly. The tree is relative to the home directory of the user building it (noted  $\sim$ / or  $\mathsf{SHOME}$ /). Only the source directory needs to be manually created by the user, all others will be automatically created either by  $\mathsf{ccb}$  or the build system.

| Sources              |                                                                     |  |  |  |  |

|----------------------|---------------------------------------------------------------------|--|--|--|--|

| Sources root         | ~/coriolis-2.x/src                                                  |  |  |  |  |

| under git            | ~/coriolis-2.x/src/coriolis                                         |  |  |  |  |

|                      |                                                                     |  |  |  |  |

| Architecture Dependa | ant Build                                                           |  |  |  |  |

|                      |                                                                     |  |  |  |  |

| Linux, SL 7, 64b     | ~/coriolis-2.x/Linux.el7_64/Release.Shared/build/ <tool></tool>     |  |  |  |  |

| Linux, SL 6, 32b     | ~/coriolis-2.x/Linux.slsoc6x/Release.Shared/build/ <tool></tool>    |  |  |  |  |

| Linux, SL 6, 64b     | ~/coriolis-2.x/Linux.slsoc6x_64/Release.Shared/build/ <tool></tool> |  |  |  |  |

| Linux, Fedora, 64b   | ~/coriolis-2.x/Linux.fc_64/Release.Shared/build/ <tool></tool>      |  |  |  |  |

| Linux, Fedora, 32b   | ~/coriolis-2.x/Linux.fc/Release.Shared/build/ <tool></tool>         |  |  |  |  |

| FreeBSD 8, 32b       | ~/coriolis-2.x/FreeBSD.8x.i386/Release.Shared/build/ <tool></tool>  |  |  |  |  |

| FreeBSD 8, 64b       | ~/coriolis-2.x/FreeBSD.8x.amd64/Release.Shared/build/ <tool></tool> |  |  |  |  |

| Windows 7, 32b       | ~/coriolis-2.x/Cygwin.W7/Release.Shared/build/ <tool></tool>        |  |  |  |  |

| Windows 7, 64b       | ~/coriolis-2.x/Cygwin.W7_64/Release.Shared/build/ <tool></tool>     |  |  |  |  |

| Windows 8.x, 32b     | ~/coriolis-2.x/Cygwin.W8/Release.Shared/build/ <tool></tool>        |  |  |  |  |

| Windows 8.x, 64b     | ~/coriolis-2.x/Cygwin.W8_64/Release.Shared/build/ <tool></tool>     |  |  |  |  |

| Architecture Dependa | ant Install                                                         |  |  |  |  |

| Linux, SL 6, 32b     | ~/coriolis-2.x/Linux.slsoc6x/Release.Shared/install/                |  |  |  |  |

| FHS Compliant Struct | ure under Install                                                   |  |  |  |  |

|                      |                                                                     |  |  |  |  |

| Binaries             | /install/bin                                                        |  |  |  |  |

| Libraries (Python)   | /install/lib                                                        |  |  |  |  |

| Include by tool      | /install/include/coriolis2/ <project>/<tool></tool></project>       |  |  |  |  |

| Configuration files  | /install/etc/coriolis2/                                             |  |  |  |  |

| Doc, by tool         | /install/share/doc/coriolis2/en/html/ <tool></tool>                 |  |  |  |  |

## Note

Alternate build types: the Release. Shared means an optimized build with shared libraries. But there are also available Static instead of Shared and Debug instead of Release and any combination of them.

Static do not work because I don't know yet to mix statically linked binaries and Python modules (which must be dynamic).

## **Building Coriolis**

First step is to install the prerequisites. Currently, only RapidJSON. As RapidJSON is evolving fast, if you encounter compatibility problems, the exact version we compiled against is given below.

```

dummy@lepka:~> mkdir -p ~/coriolis-2.x/src/support

dummy@lepka:~> cd ~/coriolis-2.x/src/support

dummy@lepka:~> git clone http://github.com/miloyip/rapidjson

dummy@lepka:~> git checkout ec322005072076ef53984462fb4a1075c27c7dfd

```

The second step is to create the source directory and pull the git repository:

```

dummy@lepka:~> mkdir -p ~/coriolis-2.x/src

dummy@lepka:~> cd ~/coriolis-2.x/src

dummy@lepka:~> git clone https://www-soc.lip6.fr/git/coriolis.git

```

Third and final step, build & install:

We need to separate to perform a separate installation of the documentation because it do not support to be generated with a parallel build. So we compile & install in a first stage in -j4 (or whatever) then we generate the documentation in -j1

Under RHEL6 or clones, you must build using the **devtoolset2**:

If you want to uses Qt 5 instead of Qt 4, you may add the --qt5 argument.

The complete list of **ccb** functionalities can be accessed with the --help argument. It also may be run in graphical mode (--gui).

#### **Building the Devel Branch**

In the Coriolis git repository, two branches are present:

- The master branch, which contains the latest stable version. This is the one used by default if you follow the above instructions.

- The **devel** branch, which obviously contains the latest commits from the development team. To use it instead of the **master** one, do the following command just after the first step:

Be aware that it may requires newer versions of the dependencies and may introduce incompatibilities with the stable version.

In the (unlikely) event of a crash of  ${\tt cgt}$  , as it is a PYTHON script, the right command to run  ${\tt gdb}$  on it is:

```

dummy@lepka:work> gdb python core.XXXX

```

#### **Additionnal Requirement under MACOS**

CORIOLIS make uses of the **boost::python** module, but the MACPORTS **boost** seems unable to work with the PYTHON bundled with MACOS. So you have to install both of them from MACPORTS.

```

dummy@macos:~> port install boost +python27

dummy@macos:~> port select python python27

dummy@macos:-> export DYLD_FRAMEWORK_PATH=/opt/local/Library/Frameworks

```

The last two lines tell MacOS to use the PYTHON from MacPorts and *not* from the system. Then proceed with the generic install instructions.

## **Packaging Coriolis**

Packager should not uses **ccb**, instead bootstrap/Makefile.package is provided to emulate a top-level autotool makefile. Just copy it in the root of the CORIOLIS git repository (~/corriolis-2.x/src/coriolis/) and build.

Sligthly outaded packaging configuration files can also be found under bootstrap/:

- bootstrap/coriolis2.spec.in for **rpm** based distributions.

- bootstrap/debian for DEBIAN based distributions.

## Hooking up into ALLIANCE

CORIOLIS relies on ALLIANCE for the cell libraries. So after installing or packaging, you must configure it so that it can found those libraries.

This is done by editing the one variable **cellsTop** in the ALLIANCE helper (see **Alliance Helper**). This variable must point to the directory of the cells libraries. In a typical installation, this is generally **/usr/share/alliance/cells**.

#### Setting up the Environment (coriolisEnv.py)

To simplify the tedious task of configuring your environment, a helper is provided in the bootstrap source directory (also installed in the directory . . . /install/etc/coriolis2/):

```

~/coriolis-2.x/src/coriolis/bootstrap/coriolisEnv.py

```

Use it like this:

```

dummy@lepka:~> eval `~/coriolis-2.x/src/coriolis/bootstrap/coriolisEnv.py`

```

#### Note

**Do not call that script in your environement initialisation.** When used under RHEL6 or clones, it needs to be run in the **devtoolset2** environement. The script then launch a new shell, which may cause an infinite loop if it's called again in, say **~/.bashrc**. Instead you may want to create an alias:

alias c2r='eval "`~/coriolis-2.x/src/coriolis/bootstrap/coriolisEnv.py`"'

## **Coriolis Configuration & Initialisation**

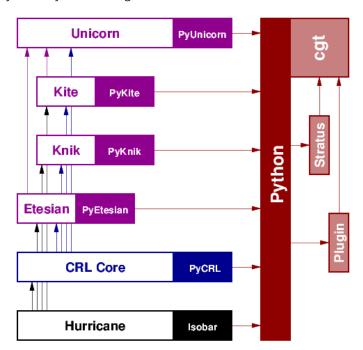

#### **General Software Architecture**

CORIOLIS has been build with respect of the classical paradigm that the computational instensive parts have been written in C++, and almost everything else in PYTHON. To build the PYTHON interface we used two methods:

- For self-contained modules boost::python (mainly in vlsisapd).

- For all modules based on HURRICANE, we created our own wrappers due to very specific requirements such as shared functions between modules or C++/PYTHON secure bidirectional object deletion.

#### Note

**Python Documentation:** Most of the documentation is related to the C++ API and implementation of the tools. However, the PYTHON bindings have been created so they mimic as closely as possible the C++ interface, so the documentation applies to both languages with only minor syntactic changes.

All configuration & initialization files are Python scripts, despite their .conf extention. From a syntactic point of view, there is no difference between the system-wide configuration files and the user's configuration, they may use the same Python helpers.

Configuration is done in two stages:

- 1. Selecting the symbolic technology.

- 2. Loading the complete configuration for the given technology.

## **First Stage: Technology Selection**

The initialization process is done by executing, in order, the following file(s):

| Order | Meaning                   | File                             |

|-------|---------------------------|----------------------------------|

| 1     | The system setting        | /etc/coriolis2/techno.conf       |

| 2     | The user's global setting | \${HOME}/.coriolis2/techno.py    |

| 3     | The user's local setting  | <cwd>/.coriolis2/techno.py</cwd> |

Thoses files must provides only one variable, the name of the technology. Each technology will provide configuration for both the symbolic part and the real part. Coriolis can work with purely symbolic technology (symbolic/cmos) in that case, the real technology part is a dummy one

For example, to use Mosis 18onm:

```

# -*- Mode:Python -*-

technology = '180/scn6m_deep_09'

```

## **Second Stage: Technology Configuration Loading**

The **TECHNO** variable is set by the first stage and it's the name of the symbolic technology. A directory of that name, with all the configuration files, must exists in the configuration directory. In addition to the technology-specific directories, a **common/** directory is there to provides a trunk for all the identical datas across the various technologies. The initialization process is done by executing, in order, the following file(s):

| Order | Meaning                          | File                                            |       |

|-------|----------------------------------|-------------------------------------------------|-------|

| 1     | The system initialization        | /etc/coriolis2/ <techno>/<tool></tool></techno> | .conf |

| 2     | The user's global initialization | \${HOME}/.coriolis2/settings.py                 |       |

| 3     | The user's local initialization  | <cwd>/.coriolis2/settings.py</cwd>              |       |

#### Note

The loading policy is not hard-coded. It is implemented at Python level in /etc/coriolis2/coriolisInit.py, and thus may be easily be amended to whatever site policy.

The truly mandatory requirement is the existence of **coriolisInit.py** which *must* contain a **coriolisConfigure()** function with no argument.

## **Configuration Helpers**

To ease the writing of configuration files, a set of small helpers is available. They allow to setup the configuration parameters through simple assembly of tuples. The helpers are installed under the directory:

<install>/etc/coriolis2/

Where **<install>**/ is the root of the installation.

#### **ALLIANCE Helper**

The configuration file must provide a **allianceConfig** tuple of the form:

```

cellsTop = '/usr/share/alliance/cells/'

allianceConfig = \

( ( 'SYMBOLIC_TECHNOLOGY', helpers.sysConfDir+'/technology.symbolic.xml'

, ( 'REAL_TECHNOLOGY' , helpers.sysConfDir+'/technology.cmos130.s2r.xml')

, ('DISPLAY'

, helpers.sysConfDir+'/display.xml'

)

, ('CATALOG' , 'CATAL')

, ('WORKING_LIBRARY' , '.')

, ('SYSTEM_LIBRARY' , ((cellsTop+'sxlib' , Environment.Append)

, ( 'CATALOG'

, (cellsTop+'dp_sxlib', Environment.Append)

, (cellsTop+'ramlib' , Environment.Append)

, (cellsTop+'romlib' , Environment.Append)

, (cellsTop+'rflib' , Environment.Append)

, (cellsTop+'rf2lib' , Environment.Append)

, (cellsTop+'pxlib' , Environment.Append) ) )

, 100)

, ( 'SCALE_X'

, 'vst')

, ('IN_LO'

, 'ap')

, ( 'IN_PH'

, 'vst')

, 'ap')

, ( 'OUT_LO'

, ( 'OUT_PH'

, ('POWER'

, 'vdd')

, 'vss')

, '^ck.*')

, ('GROUND'

, ('CLOCK'

, ( 'BLOCKAGE'

, '^blockageNet*')

```

The example above shows the system configuration file, with all the available settings. Some important remarks about thoses settings:

- In it's configuration file, the user do not need to redefine all the settings, just the one he wants to change. In most of the cases, the SYSTEM\_LIBRARY, the WORKING\_LIBRARY and the special net names (at this point there is not much alternatives for the others settings).

- SYSTEM\_LIBRARY setting: Setting up the library search path. Each library entry in the tuple will be added to the search path according to the second parameter:

- Environment:: Append: append to the search path.

- **Environment::Prepend**: insert in head of the search path.

- Environment::Replace: look for a library of the same name and replace it, whithout changing the search path order. If no library of that name already exists, it is appended.

A library is identified by it's name, this name is the last component of the path name. For instance: /soc/alliance/sxlib will be named sxlib. Implementing the ALLIANCE specification, when looking for a *Cell* name, the system will browse sequentially trought the library list and returns the first *Cell* whose name match.

- For POWER, GROUND, CLOCK and BLOCKAGE net names, a regular expression (GNU regexp) is expected.

- The helpers.sysConfDir variable is supplied by the helpers, it is the directory in which the system-wide configuration files are locateds. For a standard installation it would be: /soc/coriolis2.

A typical user's configuration file would be:

```

import os

homeDir = os.getenv('HOME')

allianceConfig = \

( ('WORKING_LIBRARY' , homeDir+'/worklib')

, ('SYSTEM_LIBRARY' , (homeDir+'/mylib', Environment.Append) ) )

, ('POWER' , 'vdd.*')

, ('GROUND' , 'vss.*')

```

## **Tools Configuration Helpers**

All the tools uses the same helper to load their configuration (a.k.a. *Configuration Helper*). Currently the following configuration system-wide configuration files are defined:

- misc.conf: commons settings or not belonging specifically to a tool.

- etesian.conf: for the ETESIAN tool.

- kite.conf: for the KITE tool.

- stratus1.conf: for the STRATUS1 tool.

Here is the contents of etesian.conf:

```

# Etesian parameters.

parametersTable = \

( ('etesian.aspectRatio' , TypePercentage, 100 , { 'min':10, 'max':1000 } )

, ('etesian.spaceMargin' , TypePercentage, 5 )

, ('etesian.uniformDensity', TypeBool , False ), ('etesian.routingDriven', TypeBool , False )

, ("Standard", 2)

, ("High" , 3)

, ("Extreme" , 4) ) }

)

, ("etesian.graphics" , TypeEnumerate , 2

, { 'values':( ("Show every step" , 1)

, ("Show lower bound" , 2)

, ("Show result only" , 3) ) }

)

layoutTable = \

( (TypeTab , 'Etesian', 'etesian')

, (TypeTitle , 'Placement area')

, (TypeOption, "etesian.aspectRatio" , "Aspect Ratio, X/Y (%)", 0 )

, (TypeOption, "etesian.spaceMargin" , "Space Margin" , 1)

, (TypeRule ,)

, (TypeTitle , 'Etesian - Placer')

, (TypeOption, "etesian.uniformDensity", "Uniform density"

, 0 )

, (TypeOption, "etesian.routingDriven", "Routing driven"

, 0 )

, (TypeOption, "etesian.effort" , "Placement effort" , "Placement view"

, 1 )

, (TypeRule ,)

```

Taxonomy of the file:

- It must contains, at least, the two tables:

- parametersTable, defines & initialise the configuration variables.

- layout Tables, defines how the various parameters will be displayed in the configuration window (The Settings Tab).

- The parametersTable, is a tuple (list) of tuples. Each entry in the list describe a configuration parameter. In it's simplest form, it's a quadruplet (TypeOption, 'paramId', ParameterType, DefaultValue) with:

- 1. TypeOption, tells that this tuple describe a parameter.

- 2. paramId, the identifier of the parameter. Identifiers are defined by the tools. The list of parameters is detailed in each tool section.

- 3. ParameterType, the kind of parameter. Could be:

- TypeBool, boolean.

- TypeInt, signed integer.

- TypeEnumerate, enumerated type, needs extra entry.

- TypePercentage, percentage, expressed between o and 100.

- TypeDouble, float.

- TypeString, character string.

- 4. Default Value, the default value for that parameter.

## **Hacking the Configuration Files**

Asides from the symbols that gets used by the configuration helpers like **allianceConfig** or **parametersTable**, you can put pretty much anything in **<CWD>/.coriolis2/settings.py** (that is, written in PYTHON).

For example:

```

# -*- Mode:Python -*-

defaultStyle = 'Alliance.Classic [black]'

# Regular Coriolis configuration.

parametersTable = \

( ('misc.catchCore' , TypeBool

, ('misc.info' , TypeBool

, ('misc.paranoid' , TypeBool

, ('misc.bug' , TypeBool

, ('misc.logMode' , TypeBool

, ('misc.verboseLevel1' , TypeBool

, ('misc.verboseLevel2' , TypeBool

, ('misc.minTraceLevel' , TypeInt

, ('misc.maxTraceLevel' , TypeInt

, False )

, False

, False

, False

, True

, False )

, True )

, 0

)

# Some ordinary Python script...

import os

print ' o Cleaning up ClockTree previous run.'

for fileName in os.listdir('.'):

if fileName.endswith('.ap') or (fileName.find('_clocked.') >= 0):

- <%s>' % fileName

print '

os.unlink(fileName)

```

See Python Interface to Coriolis for more details those capabilities.

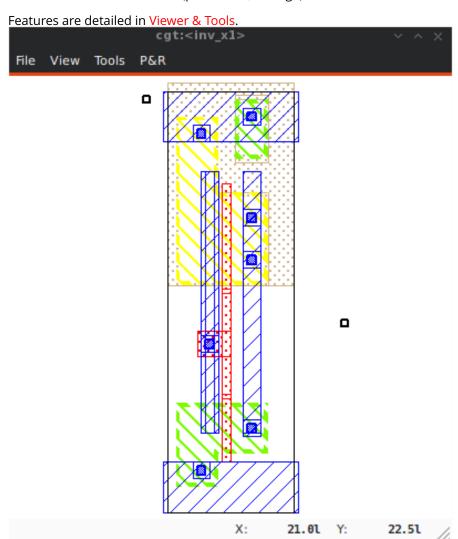

## **CGT - The Graphical Interface**

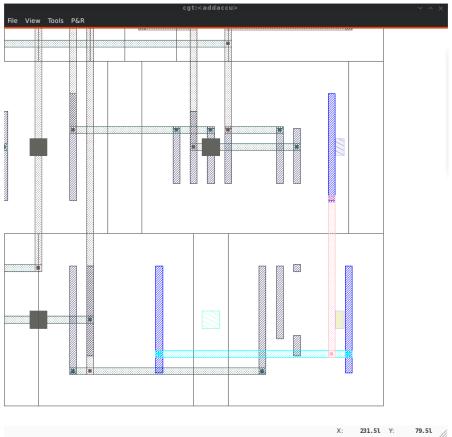

The Coriolis graphical interface is split up into two windows.

- The **Viewer**, with the following features:

- · Basic load/save capabilities.

- Display the current working cell. Could be empty if the design is not yet placed.

- Execute Stratus Scripts.

- Menu to run the tools (placement, routage).

- The Controller, which allows:

- Tweak what is displayer by the *Viewer*. Through the *Look, Filter* and *Layers&Gos* tabs.

- Browse the *netlist* with eponym tab.

- Show the list of selected objects (if any) with selection

- Walk through the Database, the Cell or the Selection with *Inspector*. This is an advanced feature, reserved for experimented users.

- The tab *Settings* which give access to all the settings. They are closely related to Configuration & Initialisation.

#### **Viewer & Tools**

#### **STRATUS Netlist Capture**

STRATUS is the replacement for GENLIB procedural netlist capture language. It is designed as a set of PYTHON classes, and comes with it's own documentation (Stratus Documentation)

#### The HURRICANE Data-Base

The ALLIANCE flow is based on the MBK data-base, which has one data-structure for each view. That is, **Lofig** for the *logical* view and **Phfig** for the *physical* view. The place and route tools were responsible for maintaining (or not) the coherency between views. Reflecting this weak coupling between views, each one was stored in a separate file with a specific format. The *logical* view is stored in a **vst** file in VHDL format and the *physical* in an **ap** file in an ad-hoc format.

The Coriolis flow is based on the Hurricane data-base, which has a unified structure for *logical* and *physical* view. That data structure is the *Cell* object. The *Cell* can have any state between pure netlist and completly placed and routed design. Although the memory representation of the views has deeply changed we still use the Alliance files format, but they now really represent views of the same object. The point is that one must be very careful about view coherency when going to and from Coriolis.

As for the second release, CORIOLIS can be used only for three purposes:

- **Placing a design**, in which case the *netlist* view must be present.

- **Routing a design**, in that case the *netlist* view and the *layout* view must be present and *layout* view must contain a placement. Both views must have the same name. When saving the routed design, it is advised to change the design name otherwise the original unrouted placement in the *layout* view will be overwritten.

• **Viewing a design**, the *netlist* view must be present, if a *layout* view is present it still must have the same name but it can be in any state.

#### Synthetizing and loading a design

CORIOLIS supports several file formats. It can load all file format from the ALLIANCE toolchain (.ap for layout, behavioural and structural vhdl .vbe and .vst), BLIF netlist format as well as benchmark formats from the ISPD contests.

It can be compiled with LEF/DEF support, although it requires acceptance of the SI2 license and may not be compiled in your version of the software.

**Synthesis under Yosys** You can create a BLIF file from the Yosys synthetizer, which can be imported under Coriolis. Most libraries are specified as a .lib liberty file and a .lef LEF file. Yosys opens most .lib files with minor modifications, but LEF support in Coriolis relies on SI2. If Coriolis hasn't been compiled against it, the library is given in ALLIANCE .ap format. Some free libraries already provide both .ap and .lib files.

Once you have installed a common library under Yosys and Coriolis, just synthetize your design with Yosys and import it (as Blif without the extension) under Coriolis to perform place&route.

**Synthesis under Alliance** Alliance is an older toolchain but has been extensively used for years. Coriolis can import and write Alliance designs and libraries directly.

#### **Etesian -- Placer**

The ETESIAN placer is a state of the art (as of 2015) analytical placer. It is within 5% of other placers' solutions, but is normally a bit worse than ePlace. This CORIOLIS tool is actually an encapsulation of COLOQUINTE which *is* the placer.

#### Note

*Instance Uniquification Unsupported:* a same logical instance cannot have two different placements. So, either you manually make a clone of it or you supply a placement for it. We need to implement uniquification in the Hurricane database.

#### **Hierarchical Placement**

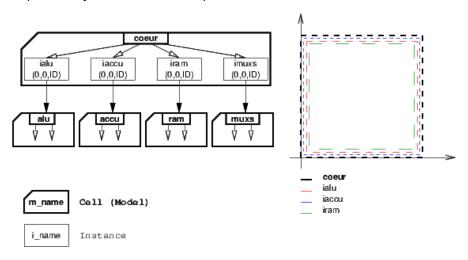

The placement area is defined by the top cell abutment box.

When placing a complete hierarchy, the abutment boxes of the cells (models) other than the top cell are sets identical to the one of the top cell and their instances are all placed at position  $(0,0,\mathbb{ID})$ . That is, all the abutments boxes, whatever the hierarchical level, defines the same area (they are exactly superposed).

We choose this scheme because the placer will see all the instances as virtually flattened, so they can be placed anywhere inside the top-cell abutment box.

#### **Computing the Placement Area**

The placement area is computed using the <code>etesian.aspectRatio</code> and <code>etesian.spaceMargin</code> parameters only if the top-cell has an empty abutment box. If the top-cell abutment box has to be set, then it is propagated to all the instances models recursively.

#### **Reseting the Placement**

Once a placement has been done, the placer cannot reset it (will be implemented later). To perform a new placement, you must restart **cgt** . In addition, if you have saved the placement on disk, you must erase any **.ap** file, which are automatically reloaded along with the netlist (.vst).

#### Limitations

Etesian supports standard cells and fixed macros. As for the Coriolis 2.1 version, it doesn't support movable macros, and you must place every macro beforehand. Timing and routability analysis are not included either, and the returned placement may be unroutable.

## **Etesian Configuration Parameters**

| Parameter Identifier   | Туре                                                                              | Default                                                                    |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| Etesian Parameters     |                                                                                   |                                                                            |  |  |  |  |

| etesian.aspectRatio    | TypePercentage                                                                    | 100                                                                        |  |  |  |  |

| etesian.aspectratio    | Define the height on width H/W aspect ratio, can be comprised between 10 and 1000 |                                                                            |  |  |  |  |

| etesian.spaceMargin    | TypePercentage                                                                    | 5                                                                          |  |  |  |  |

| cccsian.spacemargin    | The extra white sarea of the stand                                                | space added to the total<br>ard cells                                      |  |  |  |  |

| etesian.uniformDensity | TypeBool                                                                          | False                                                                      |  |  |  |  |

|                        |                                                                                   | s will be spread envenly<br>r allowed to form denser                       |  |  |  |  |

| etesian.effort         | TypeInt                                                                           | 2                                                                          |  |  |  |  |

| cccsian.criore         | Sets the balance between the speed of the placer and the solution quality         |                                                                            |  |  |  |  |

| etesian.routingDriven  | TypeBool                                                                          | False                                                                      |  |  |  |  |

| cccstan.roucingbriven  | tions and white                                                                   | ol will try routing itera-<br>space allocation to im-<br>to be implemented |  |  |  |  |

| etesian.graphics       | TypeInt                                                                           | 2                                                                          |  |  |  |  |

| eccolum.grupmico       | How often the of More refreshing s                                                | lisplay will be refreshed<br>slows the placer.                             |  |  |  |  |

|                        | • 1 shows l<br>bounds                                                             | ooth upper and lower                                                       |  |  |  |  |

|                        | • 2 only show                                                                     | s lower bound results                                                      |  |  |  |  |

|                        | • 3 only show                                                                     | vs the final results                                                       |  |  |  |  |

#### **Knik -- Global Router**

The quality of KNIK global routing solutions are equivalent to those of FGR 1.0. For an in-depth description of KNIK algorithms, you may download the thesis of D. Dupuls avalaible from here~: Knik Thesis.

The global router is (not yet) deterministic. To circumvent this limitation, a global routing *solution* can be saved to disk and reloaded for later uses.

A global routing is saved into a file with the same name as the design and a **kgr** extention. It is in Box Router output format.

Menus:

- P&R ightarrow Step by Step ightarrow Save Global Routing

- P&R ightarrow Step by Step ightarrow Load Global Routing

#### **Kite -- Detailed Router**

KITE no longer suffers from the limitations of Nero . It can route big designs as its runtime and memory footprint is almost linear (with respect to the number of gates). It has successfully routed design of more than 150K gates.

However, this first release comes with the temporary the following restrictions:

- Works only with SXLIB standard cell gauge.

- Works always with 4 routing metal layers (M2 through M5).

- ullet Do not allow (take into account) pre-routed wires on signals other than POWER or GROUND

#### Note

**Slow Layer Assignment.** Most of the time, the layer assignment stage is fast (less than a dozen seconds), but in some instances it can take more than a dozen *minutes*. This is a known bug and will be corrected in later releases.

After each run, KITE displays a set of *completion ratios* which must all be equal to 100% if the detailed routing has been successfull. In the event of a failure, on a saturated design, you may decrease the *edge saturation ratio* (argument --edge) to balance more evenly the design saturation. That is, the maximum saturation decrease at the price of a wider saturated area and increased wirelength. This is the saturation of the *global* router KNIK, and you may increase/decrease by steps of 5%, which represent one track. The maximum capacity of the SXLIB gauge is 10 tracks in two layers, that makes 20 tracks by KNIK edge.

Routing a design is done in four ordered steps:

- 1. Detailed pre-route  $P&R \rightarrow Step$  by  $Step \rightarrow Detailed$  PreRoute

- 2. Global routing  $P&R \rightarrow Step\ by\ Step \rightarrow Global\ Route$

- 3. Detailed routing  $P&R \rightarrow Step by Step \rightarrow Detailed Route$

- 4. Finalize routing  $P&R \rightarrow Step by Step \rightarrow Finalize Route$

It is possible to supply to the router a complete wiring for some nets that the user's wants to be routed according to a specific topology. The supplied topology must respect the building rules of the KATABATIC database (contacts must be, terminals, turns, h-tee & v-tee only). During the first step <a href="Detailed Pre-Route">Detailed Pre-Route</a> the router will solve overlaps between the segments, without making any dogleg. If no pre-routed topologies are present, this step may be ommited. Any net routed at this step is then fixed and become unmovable for the later stages.

After the detailed routing step the KITE data-structure is still active (the Hurricane wiring is decorated). The finalize step performs the removal of the KITE data-structure, and it is not advisable to save the design before that step.

You may visualize the density (saturation) of either KNIK (on edges) or KITE (on GCells) until the routing is finalized. Special layers appears to that effect in the The Layers&Go Tab.

**Kite Configuration Parameters** As KNIK is only called through KITE, it's parameters also have the **kite**. prefix.

The KATABATIC parameters control the layer assignment step.

All the defaults value given below are from the default ALLIANCE technology (cmos and SxLib cell gauge/routing gauge).

| Parameter Identifier        | Туре                                                                                | Default                                 |  |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Katabatic Parameters        |                                                                                     |                                         |  |  |  |  |  |

| katabatic.topRoutingLa      | y eTrypeString                                                                      | METAL5                                  |  |  |  |  |  |

|                             |                                                                                     | st metal layer that will be             |  |  |  |  |  |

|                             | used for routing                                                                    | (inclusive).                            |  |  |  |  |  |

| katabatic.globalLength      | Th <b>TrypeInt</b> ld                                                               | 1450                                    |  |  |  |  |  |

|                             |                                                                                     | s used by a layer assign-               |  |  |  |  |  |

|                             | ment method which is no longe                                                       |                                         |  |  |  |  |  |

| katabatic.saturateRati      | not give good res                                                                   |                                         |  |  |  |  |  |

| Ratabatic.SaturateRati      | J                                                                                   | <b>80</b><br>is above this ratio, move  |  |  |  |  |  |

|                             |                                                                                     | bal segments up from                    |  |  |  |  |  |

|                             | depth x to x+2                                                                      |                                         |  |  |  |  |  |

| landa de de la contracta De | TypeInt                                                                             | 8                                       |  |  |  |  |  |

| katabatic.saturateRp        | If a GCell co                                                                       | ntains more terminals                   |  |  |  |  |  |

|                             |                                                                                     | han that number, force a                |  |  |  |  |  |

|                             | those in excess                                                                     | connecting segments to                  |  |  |  |  |  |

| Knik Parameters             | those in excess                                                                     |                                         |  |  |  |  |  |

|                             | -Typolnt                                                                            | 2                                       |  |  |  |  |  |

| kite.hTracksReservedLo      |                                                                                     | 3<br>:he tracks needed <i>inside</i> a  |  |  |  |  |  |

|                             |                                                                                     | e <i>local</i> routing, decrease        |  |  |  |  |  |

|                             | the capacity of the edges of the global router. Horizontal and vertical locally re- |                                         |  |  |  |  |  |

|                             |                                                                                     |                                         |  |  |  |  |  |

|                             | served capacity can be distinguished for                                            |                                         |  |  |  |  |  |

|                             | more accuracy.                                                                      |                                         |  |  |  |  |  |

| kite.vTracksReservedLo      |                                                                                     | 3                                       |  |  |  |  |  |

| Vita Banana tana            | CT. kite.hTrac                                                                      | ksReservedLocal                         |  |  |  |  |  |

| Kite Parameters             | T a lock                                                                            | 400000                                  |  |  |  |  |  |

| kite.eventsLimit            | TypeInt                                                                             | 4000002                                 |  |  |  |  |  |

|                             | The maximum number of segment displacements, this is a last ditch safety            |                                         |  |  |  |  |  |

|                             |                                                                                     | oop. It's perhaps a little              |  |  |  |  |  |

|                             | too low for big d                                                                   |                                         |  |  |  |  |  |

| kite.ripupCost              | TypeInt                                                                             | 3                                       |  |  |  |  |  |

| kite:Tipupcost              |                                                                                     | duced between two ripup                 |  |  |  |  |  |

|                             | I .                                                                                 | cost to avoid a loop between two ripped |  |  |  |  |  |

|                             | up segments                                                                         | T                                       |  |  |  |  |  |

| kite.strapRipupLimit        | TypeInt                                                                             | 16                                      |  |  |  |  |  |

|                             | Maximum numb                                                                        | er of ripup for <i>strap</i> seg-       |  |  |  |  |  |

|                             | TypeInt                                                                             | 9                                       |  |  |  |  |  |

| kite.localRipupLimit        |                                                                                     | er of ripup for <i>local</i> seg-       |  |  |  |  |  |

|                             | ments                                                                               | iei oi lihah ioi <i>locai</i> seg-      |  |  |  |  |  |

|                             |                                                                                     | continued on poyt page                  |  |  |  |  |  |

... continued on next page

| Parameter Identifier    | Туре                                                                                                            | Default                                                                            |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| kite.globalRipupLimit   | TypeInt                                                                                                         | 5                                                                                  |  |  |  |

| Kite.globalNipupiimit   | Maximum number of ripup for <i>global</i> segments, when this limit is reached, triggers topologic modification |                                                                                    |  |  |  |

| kite.longGlobalRipupLin | ni⊞ypelnt                                                                                                       | 5                                                                                  |  |  |  |

|                         |                                                                                                                 | er of ripup for <i>long global</i><br>this limit is reached, trig-<br>nodification |  |  |  |

#### **Executing Python Scripts in Cgt**

Python/Stratus scripts can be executed either in text or graphical mode.

#### Note

**How Cgt Locates Python Scripts:** cgt uses the Python import mechanism to load Python scripts. So you must give the name of your script whitout .py extention and it must be reachable through the PYTHONPATH. You may uses the dotted module notation.

A Python/Stratus script must contains a function called <code>ScriptMain()</code> with one optional argument, the graphical editor into which it may be running (will be set to <code>None</code> in text mode). The Python interface to the editor (type: <code>CellViewer</code>) is limited to basic capabilities only.

Any script given on the command line will be run immediatly *after* the initializations and *before* any other argument is processed.

For more explanation on Python scripts see Python Interface to Coriolis.

#### **Printing & Snapshots**

Printing or saving into a PDF is fairly simple, just uses the **File -> Print** menu or the CTRL+P shortcut to open the dialog box.

The print functionality uses exactly the same rendering mechanism as for the screen, beeing almost WYS/WYG. Thus, to obtain the best results it is advisable to select the Coriolis.Printer look (in the Controller), which uses a white background and much suited for high resolutions  $32 \times 32$  pixels patterns

There is also two mode of printing selectable through the *Controller* **Settings** -> **Misc** -> **Printer/Snapshot Mode**:

| Mode           | DPI (approx.) | Intended Usage                                                                             |

|----------------|---------------|--------------------------------------------------------------------------------------------|

| Cell Mode      | 150           | For single Cell printing or very small designs. Patterns will be bigger and more readable. |

| Design<br>Mode | 300           | For designs (mostly commposed of wires and cells outlines).                                |

#### Note

The pdf file size Be aware that the generated PDF files are indeed only pixmaps. So they can grew very large if you select paper format above A2 or similar.

Saving into an image is subject to the same remarks as for PDF.

#### **Memento of Shortcuts in Graphic Mode**

The main application binary is cgt.

| Category   | Keys             | Action                                                                                                                                                                                                                                                                                                                    |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Moves      |                  | Shift the view in the according direction                                                                                                                                                                                                                                                                                 |

|            | Up, Down         |                                                                                                                                                                                                                                                                                                                           |

|            | Left,            |                                                                                                                                                                                                                                                                                                                           |

|            | Right            |                                                                                                                                                                                                                                                                                                                           |

| Fit        | f                | Fit to the Cell abutment box                                                                                                                                                                                                                                                                                              |

| Refresh    | CTRL+L           | Triggers a complete display redraw                                                                                                                                                                                                                                                                                        |

| Goto       | g                | apperture is the minimum side of the area displayed around the point to go to. It's an alternative way of setting the zoom level                                                                                                                                                                                          |

| Zoom       | z, m             | Respectively zoom by a 2 factor and <i>unzoom</i> by a 2 factor                                                                                                                                                                                                                                                           |

|            | Ø                | You can perform a zoom to an area. Define the zoom area by <i>holding down the left mouse button</i> while moving the mouse.                                                                                                                                                                                              |

|            | Area Zoom        |                                                                                                                                                                                                                                                                                                                           |

| Selection  | B                | You can select displayed objects under an area.  Define the selection area by holding down the right mouse button while moving the mouse.                                                                                                                                                                                 |

|            | Area Selection   |                                                                                                                                                                                                                                                                                                                           |

|            | Toggle Selection | You can toggle the selection of one object under the mouse position by pressing CTRL and pressing down <i>the right mouse button</i> . A popup list of what's under the position shows up into which you can toggle the selection state of one                                                                            |

|            |                  | item.                                                                                                                                                                                                                                                                                                                     |

| 6 1 11     | S                | Toggle the selection visibility                                                                                                                                                                                                                                                                                           |

| Controller | CTRL+I           | Show/hide the controller window.  It's the Swiss Army Knife of the viewer. From it, you can fine-control the display and inspect almost everything in your design.                                                                                                                                                        |

| Rulers     | k, ESC           | One stroke on k enters the ruler mode, in which you can draw one ruler. You can exit the ruler mode by pressing ESC. Once in ruler mode, the first click on the <i>left mouse button</i> sets the ruler's starting point and the second click the ruler's end point. The second click exits automatically the ruler mode. |

|            | K                | Clears all the drawn rulers                                                                                                                                                                                                                                                                                               |

| Print      | CTRL+P           | Currently rather crude. It's a direct copy of what's displayed in pixels. So the resulting picture will be a little blurred due to anti-aliasing mechanism.                                                                                                                                                               |

| Open/Close | CTRL+O           | Opens a new design. The design name must be given without path or extention.                                                                                                                                                                                                                                              |

|            |                  | continued on next page                                                                                                                                                                                                                                                                                                    |

... continued on next page

| Category  | Keys      | Action                                                                                                                                                                  |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | CTRL+W    | Close the current viewer window, but do not quit the application.                                                                                                       |

|           | CTRL+Q    | CTRL+Q quit the application (closing all windows).                                                                                                                      |

| Hierarchy | CTRL+Down | Go one hierarchy level down. That is, if there is an <i>instance</i> under the cursor position, load it's <i>model</i> Cell in place of the current one.                |

|           | CTRL+Up   | Go one hierarchy level up. if we have entered the current model through <code>CTRL+Down</code> reload the previous model (the one in which this model is instanciated). |

## **Cgt Command Line Options**

Appart from the obvious ——text options, all can be used for text and graphical mode.

| Arguments                               | Meaning                                                                                                                                                                                                                                                             |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -t text                                 | Instruct <b>cgt</b> to run in text mode.                                                                                                                                                                                                                            |  |

| -L log-mode                             | Disable the uses of ANSI escape sequence on the <b>tty</b> . Useful when the output is redirected to a file.                                                                                                                                                        |  |

| -c <cell> cell=<cell></cell></cell>     | The name of the design to load, without leading path or extention.                                                                                                                                                                                                  |  |

| -g load-global                          | Reload a global routing solution from disk. The file containing the solution must be named <cell>.kgr.</cell>                                                                                                                                                       |  |

| save-global                             | Save the global routing solution, into a file named <i><design>.kgr</design></i> .                                                                                                                                                                                  |  |

| -e <ratio> edge=<ratio></ratio></ratio> | Change the edge capacity for the global router, between o and 1 (KNIK ).                                                                                                                                                                                            |  |

| -G global-route                         | Run the global router (Кык ).                                                                                                                                                                                                                                       |  |

| -R detailed-route                       | Run the detailed router (KITE ).                                                                                                                                                                                                                                    |  |

| -s save-<br>design= <routed></routed>   | The design into which the routed layout will be saved. It is strongly recommanded to choose a different name from the source (unrouted) design.                                                                                                                     |  |

| events-limit= <count></count>           | The maximal number of events after which the router will stops. This is mainly a failsafe against looping. The limit is sets to 4 millions of iteration which should suffice to any design of 100K. gates. For bigger designs you may wants to increase this limit. |  |

| stratus-script= <module></module>       | Run the Python/Stratus script module. See Python Scripts in Cgt.                                                                                                                                                                                                    |  |

## Some Examples:

• Run both global and detailed router, then save the routed design :

```

> cgt -v -t -G -R --cell=design --save-design=design_kite

```

• Load a previous global solution, run the detailed router, then save the routed design :

```

> cgt -v -t --load-global -R --cell=design --save-design=design_kite

```

• Run the global router, then save the global routing solution :

```

> cgt -v -t -G --save-global --cell=design

```

#### **Miscellaneous Settings**

| Parameter Identifier        | Туре                                                                                             | Default                                           |

|-----------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Verbosity/Log Parameters    |                                                                                                  |                                                   |

| misc.info                   | TypeBool                                                                                         | False                                             |

| misc.inio                   |                                                                                                  | of <i>info</i> level message                      |

|                             | (cinfo stream)                                                                                   |                                                   |

| misc.bug                    | TypeBool                                                                                         | False                                             |

| misc.sug                    | Enable display of <i>bug</i> level message ( <b>cbu</b> stream), messages can be a little scarry |                                                   |

| misc.logMode                | TypeBool                                                                                         | False                                             |

| misc.iogMode                | If enabled, assume that the output device is not a tty and suppress any escaped sequences        |                                                   |

| misc.verboseLevel1          | TypeBool                                                                                         | True                                              |

| mise. verbosedeveri         | First level of verbosity, disable level 2                                                        |                                                   |

| misc.verboseLevel2          | TypeBool                                                                                         | False                                             |

| misc.verbosedeverz          | Second level of ve                                                                               | erbosity                                          |

| Development/Debug Parameter | rs                                                                                               |                                                   |

| misc.minTraceLevel          | TypeInt                                                                                          | 0                                                 |

| misc.maxTraceLevel          | TypeInt                                                                                          | 0                                                 |

| misc.maxiracelevei          | Display trace inf                                                                                | ormation <i>between</i> those                     |

|                             | two levels ( <b>cdebug</b> stream)                                                               |                                                   |

| misc.catchCore              | TypeBool                                                                                         | False                                             |

|                             | By default, <b>cgt</b> d<br>erate one set this                                                   | o not dump core. To gen-<br>s flag to <b>True</b> |

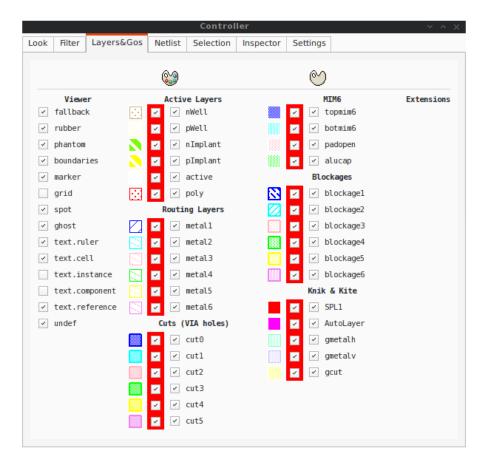

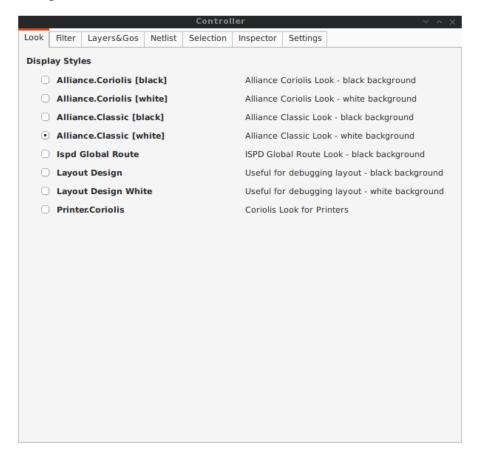

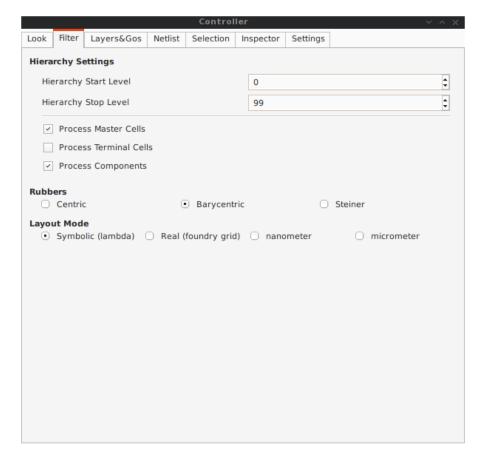

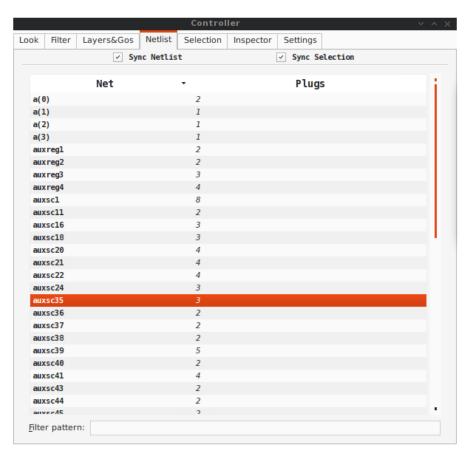

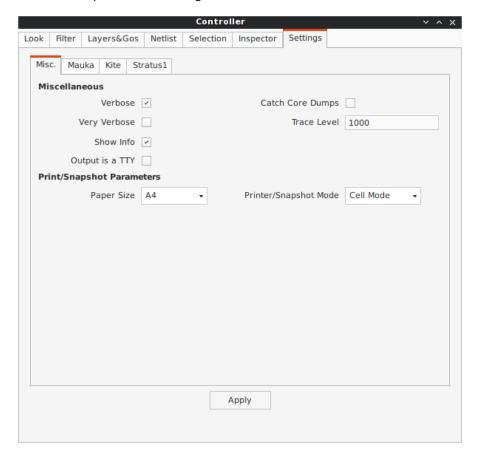

#### The Controller

The *Controller* window is composed of seven tabs:

- 1. The Look Tab to select the display style.

- 2. The Filter Tab the hierarchical levels to be displayed, the look of rubbers and the dimension units.

- 3. The Layers&Go Tab to selectively hide/display layers.

- 4. The Netlist Tab to browse through the *netlist*. Works in association with the *Selection* tab.

- 5. The Selection Tab allow to view all the currently selected elements.

- 6. The Inspector Tab browse through either the DataBase, the Cell or the current selection.

- 7. The Settings Tab access all the tool's configuration settings.

#### The Look Tab

You can select how the layout will be displayed. There is a special one Printer.Coriolis specifically designed for Printing & Snapshots. You should select it prior to calling the print or snapshot dialog boxes.

#### The Filter Tab

The filter tab let you select what hierarchical levels of your design will be displayed. Hierarchy level are numbered top-down: the level o correspond to the top-level cell, the level one to the instances of the top-level Cell and so on.

There are also check boxes to enable/disable the processing of Terminal Cell, Master Cells and Compnents. The processing of Terminal Cell (hierarchy leaf cells) is disabled by default when you load a hierarchical design and enabled when you load a single Cell.

You can choose what kind of form to give to the rubbers and the type of unit used to display coordinates.

#### Note

What are Rubbers: Hurricane uses Rubbers to materialize physical gaps in net topology. That is, if some wires are missing to connect two or more parts of net, a rubber will be drawn between them to signal the gap.

For example, after the detailed routing no *rubbers* should remains. They have been made *very* visibles as big violet lines...

#### The Layers&Go Tab

Control the individual display of all layers and Gos.

• Layers correspond to a true physical layer. From a HURRICANE point of view they are all the BasicLayers (could be matched to GDSII).

• Gos stands from Graphical Objects, they are drawings that have no physical existence but are added by the various tools to display extra information. One good exemple is the density map of the detailed router, to easily locate congested areas.

For each layer/Go there are two check boxes:

- The normal one triggers the display.

- The red-outlined allows objects of that layer to be selectable or not.

#### The Netlist Tab

The *Netlist* tab shows the list of nets... By default the tab is not *synched* with the displayed Cell. To see the nets you must check the **Sync Netlist** checkbox. You can narrow the set of displayed nets by using the filter pattern (supports regular expressions).

An very useful feature is to enable the **Sync Selection**, which will automatically select all the components of the selected net(s). You can select multiple nets. In the figure the net <code>auxsc35</code> is selected and is highlited in the *Viewer*.

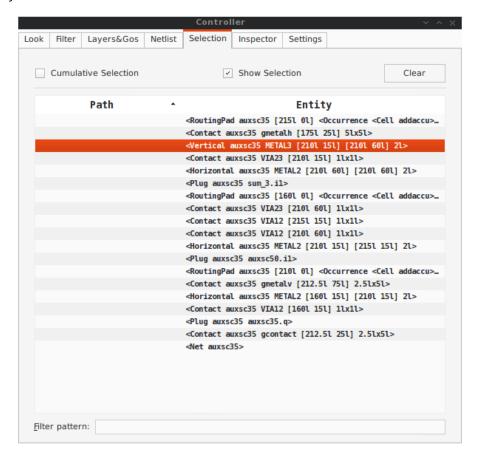

#### The Selection Tab

The *Selection* tab list all the components currently selecteds. They can be filtered thanks to the filter pattern.

Used in conjunction with the *Netlist* **Sync Selection** you will all see all the components part of *net*.

In this list, you can toggle individually the selection of component by pressing the t key. When unselected in this way a component is not removed from the the selection list but instead displayed in red italic. To see where a component is you may make it blink by repeatedly press the t key...

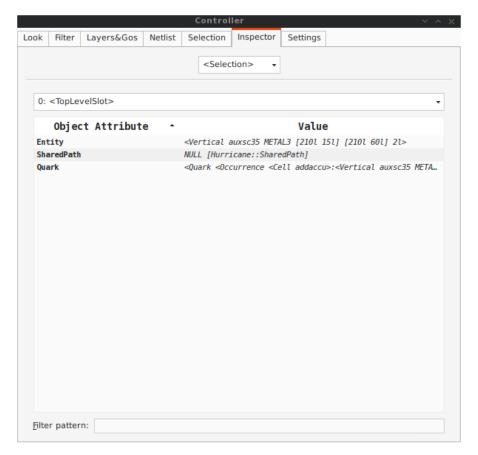

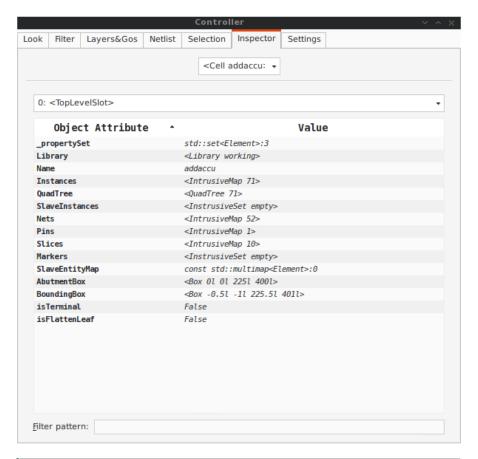

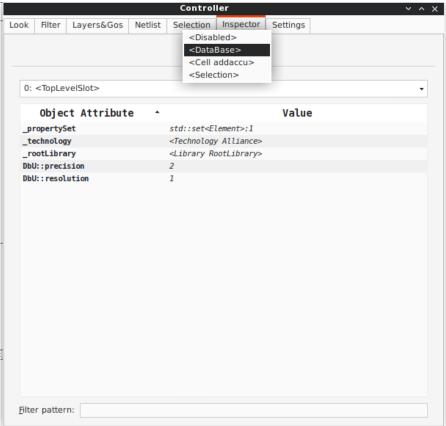

## The Inspector Tab

This tab is very useful, but mostly for Coriolis developpers. It allows to browse through the live DataBase. The *Inspector* provide three entry points:

- **DataBase**: Starts from the whole Hurricane DataBase.

- Cell: Inspect the currently loaded Cell.

- **Selection**: Inspect the object currently highlited in the *Selection* tab.

Once an entry point has been activated, you may recursively expore all it's fields using the right/left arrows.

#### Note

Do not put your fingers in the socket: when inspecting anything, do not modify the DataBase. If any object under inspection is deleted, you will crash the application...

#### Note

Implementation Detail: the inspector support is done with Slot, Record and getString().

## **The Settings Tab**

Here comes the description of the Settings tab.

## **Python Interface for Hurricane / Coriolis**

The (almost) complete interface of HURRICANE is exported as a PYTHON module and some part of the other components of CORIOLIS (each one in a separate module). The interface has been made to mirror as closely as possible the C++ one, so the C++ doxygen documentation could be used to write code with either languages.

Summary of the C++ Documentation

A script could be run directly in text mode from the command line or through the graphical interface (see Python Scripts in Cgt).

Asides for this requirement, the python script can contain anything valid in PYTHON, so don't hesitate to use any package or extention.

Small example of Python/Stratus script:

```

from Hurricane import *

from Stratus import *

def doSomething ():

# ...

return

def ScriptMain ( **kw ):

editor = None

if kw.has_key('editor') and kw['editor']:

editor = kw['editor']

stratus.setEditor( editor )

```

This typical script can be executed in two ways:

1. Run directly as a PYTHON script, thanks to the

```

if __name__ == "__main__" :

```

part (this is standart PYTHON). It is a simple adapter that will calls ScriptMain().

2. Through **cgt**, either in text or graphical mode. In that case, the **ScriptMain()** is directly called trough a sub-interpreter. The arguments of the script are passed through the \*\*kw dictionnary.

| **kw Dictionnary      |                                                                                                                                                                  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter<br>Key/Name | Contents type                                                                                                                                                    |  |

| 'cell'                | A Hurricane cell on which to work. Depending on the context, it may be None. For example, when run from cgt, it the cell currently loaded in the viewer, if any. |  |

| 'editor'              | The viewer from which the script is run, when lauched through <b>cgt</b> .                                                                                       |  |

## **Plugins**

Plugins are PYTHON scripts specially crafted to integrate with cgt. Their entry point is a ScriptMain () method as described in Python Interface to Coriolis. They can be called by user scripts through this method.

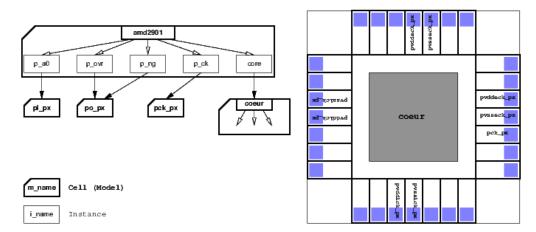

#### **Chip Placement**

Automatically perform the placement of a complete chip. This plugin, as well as the other P&R tools expect a specific top-level hierarchy for the design. The top-level hierarchy must contains the instances of all the I/O pads and **exactly one** instance of the chip's core model.

The designer must provide a configuration file that define the rules for the placement of the top-level hierarchy (that is, the pads and the core). This file must be named after the chip's name, by appending \_chip.py (obviously, it is a PYTHON file). For instance if the chip netlist file is called amd2901\_crl.vst, then the configuration file must be named amd2901\_crl\_chip.vst. Example of chip placement configuration file (for AM2901):

The file must contain one dictionnary named chip.

| Chip Dictionnary      |                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------|

| Parameter<br>Key/Name | Value/Contents type                                                                      |

| 'pad.south'           | Ordered list (left to right) of pad instances names to put on the south side of the chip |

| 'pad.east'            | Ordered list (down to up) of pad instances names to put on the east side of the chip     |

| 'pad.north'           | Ordered list (left to right) of pad instances names to put on the north side of the chip |

| 'pad.west'            | Ordered list (down to up) of pad instances names to put on the west side of the chip     |