mirror of https://github.com/lnis-uofu/SOFA.git

3.0 KiB

3.0 KiB

SOFA

Introduction

SOFA (Skywater Opensource FPGAs) are a series of open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA framework.

This repository provide the following support for the eFPGA IPs

- Architecture description file : Users can inspect architecture details and try architecture evalution using the VTR project and the OpenFPGA project.

- Fabrication-ready GDSII layouts: Users can integrate to their chip designs.

- Post-layout Verilog Netlists: Users can run HDL simulations on the eFPGA IPs to validate their applications

- Benchmark suites: An example benchmarking suite with which users can run quick examples on the eFPGA IPs

- Documentation: Datasheets for each eFPGA IPs downto circuit-level details

Quick Start

#Clone the repository and go inside it

git clone https://github.com/LNIS-Projects/skywater-openfpga.git

python3 SCRIPT/repo_setup.py --openfpga_root_path ${OPENFPGA_PROJECT_DIRECTORY}

- If you have openfpga repository cloned at the same level of this project, you can simple call

python3 SCRIPT/repo_setup.py

Otherwise, you should provide full path using the option --openfpga_root_path

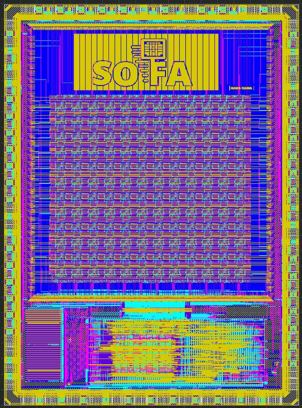

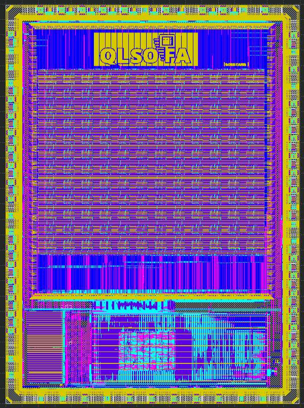

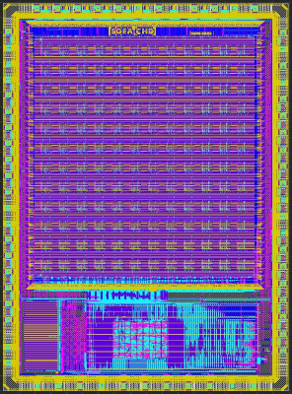

Chip Gallery

You can find a chip gallery in the online documentation.

Directory Organization

- Keep this folder clean and organized as follows

- DOC: documentation of the project

- ARCH: Architecture XML and other input files which OpenFPGA requires to generate Verilog netlists

- BENCHMARK: Benchmarks to be tested on the FPGA fabric

- HDL: Hardware description netlists for the FPGA fabrics

- SDC: design constraints

- SCRIPT: Scripts to setup, run OpenFPGA etc.

- TESTBENCH: Verilog testbenches generated by OpenFPGA

- PDK: Technology files linked from skywater opensource pdk

- SNPS_ICC2: workspace of Synopsys IC Compiler 2 Keep a README inside the folder about the ICC2 version and how-to-use.

- MSIM: workspace of verification using Mentor ModelSim

- Note:

- Please ONLY place folders under this directory. README should be the ONLY file under this directory

- Each EDA tool should have independent workspace in separated directories